## 2010 TOPCO 崇越論文大賞

論文題目:

# 利用新型光封存結構提升矽薄膜太陽能 電池元件效率

報名編號: SB0016

## 摘要

本文主要探討矽薄膜太陽能電池利用不同新型光封存結構來達到高效率低成本的太陽能電池。首先,利用雷雕機雕刻不同圖樣於 ITO 電極以達到糙化效果。第二則利用簡單的壓印法,將微結構膜仁塗佈 UV 膠壓印於太陽能電池受光面,此兩種結構皆讓光穿透進入元件後能有效增加光行走路徑與散射,進而提升元件效率。由結果得知,ITO 糙化處理與受光面壓印微結構薄膜,元件效率分別由 4.59% 提升至 5.19%與 5.99%。最後將兩種結構結合,元件效率提升幅度約 37%至 6.29%。

關鍵字:光封存結構、矽薄膜電池、太陽能電池

## 壹、緒論

為了解決日益嚴重的石化能源的消耗,目前人類對於能源的取得,仍依賴煤礦、石油、天然氣等自然資源,漸漸在自然資源慢慢消耗殆盡下,已經無法滿足人類發展需要,在使用過程中環境汙染也已經成會極待解決的嚴重問題,於是尋找替代能源已經是不容趨緩的事情,再加上「京都議定書」對溫室氣體排放之全球性管制,因此研發無污染之再生能源已是世界各國重視的課題。

目前世界各國重視的替代性能源,如:風力、水力、地熱、核能等能源中,必 須在特定地區設置,所獲得的再生能源相對有限,而太陽能電池的研發能克服地 區性的問題,能在有太陽光照射充足的地區即可設置,應用範圍相當地廣,一但 擁有設備,就可以不斷得到大自然的再生資源,因此太陽能電池被視為現今最重 要的再生資源。

自從 1950 年代,首度將太陽電池應用於人造衛星能量能源開始,太陽能電池變極具吸引力,期待太陽能電池產業的發展能解決石化、核能所帶來的環保問題,太陽能電池能使用在較充足的陽光日照,其地區性的適用非常廣泛。近幾年來,許多科技先進的國家一直對太陽能電池的研究與開發投入極大的人力與經費,期望能發展出成熟及低成本的太陽能電池製造技術,以取代目前的電力來源。

目前全世界太陽能電池產業,以矽晶圓為主的太陽能電池材料,包括單晶矽(c-Si)及多晶矽(poly-Si)晶圓(wafer)為基板的太陽能電池,佔總生產量為 80%以上,由於太陽能電池生產每年平均成長快速,大部分廠商均以單晶矽及多晶矽為主要產品,因此在人力眾多的情形下,生產技術和設備都已經相當成熟,矽晶圓太陽能電池具有高轉換效率、穩定性佳、量產速度快、壽命時間長,預期近年來,矽晶圓太陽能電池仍為市場的主流

但一般半導體產業均為矽晶的主要用戶,若其矽晶圓的需求量增大時,則極

有可能造成太陽能產業矽晶材料短缺進而價格的飆漲。以致於矽晶圓太陽能電池面臨材料成本過大的問題,一方面單晶矽或多晶矽的原料為一般的砂,即所謂的二氧化矽(SiO<sub>2</sub>),需要一定的純化技術及大規模的廠房,且製作晶圓需在高溫下溶解提煉,耗費較大量的能源及成本;另一方面,由於矽晶圓太陽能電池易脆特性,目前製造上需在 200μm 厚度以上,且使基板厚度減少的技術困難度增加,在製造大面積發電模組時對矽原料的用量相對浩大,因此要減低矽晶圓太陽能電池生產成本的可行性受到相當大的限制。

受到矽晶圓太陽能電池成本上的限制,薄膜太陽能電池的研究與開發受到各國產業的重視,由於薄膜太陽能電池對矽晶原料消耗較低,厚度可減少低於矽晶圓太陽能電池 95%以上,相當節省材料成本,可在低成本的玻璃、塑膠或不鏽鋼基板上製造,故被歸類為第二代太陽能電池。目前市場上量產的薄膜太陽能電池區分有錦化鍋(CdTe)、銅銦鎵硒(CuInGaSe2)及非晶矽(Si)材料三大類。其中以 GaAs為目前效率最高枝太陽能電池其效率可達 30%,價格昂貴且含劇毒,早期被使用於國防工業和太空衛星上,近期已有利用具光型高效率太陽能發電系統(High-concentration photovoltaic)的設計而將 GaAs 應用於民生上。而 CdTe 則因 Te 為稀有元素,且 Cd 重金屬含有劇毒有汙染的疑慮,造成商業化應用困難。實驗室研究的太陽能電池多以矽基薄膜太陽能電池為主。

矽薄膜太陽能電池的發展始自於非晶矽(amorphous silicon, a-Si:H)薄膜的製作,非晶矽優點在於可見光譜吸收能力強,可利用濺鍍或化學氣相沈積在玻璃或矽晶圓上成長薄膜,且生產過程簡易、材料成本低廉;不過缺點在於轉換效率還不及單晶/多晶矽,且在照光後容易產生嚴重的光劣化現象,即半衰期,使效率和壽命大幅降低。

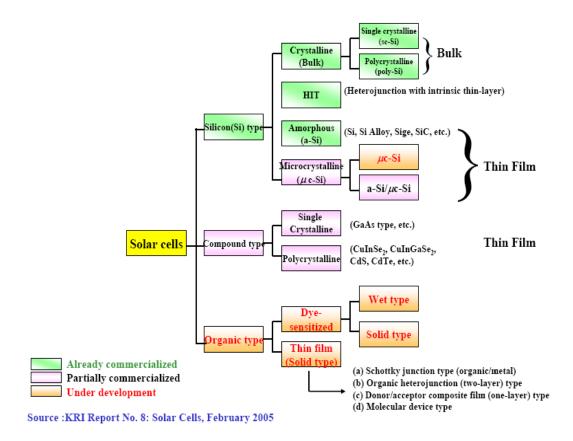

綜合上述,矽基薄膜太陽能電池提供了光伏科技的展望。當前最大的挑戰即是在如何提供可與現有的石油與核能源成本相近且兼顧低污染的光伏科技。低成本的矽基薄膜太陽能電池的發展極為其中的一個重要方向。太陽能電池依種類可分兩種:Wafer based 及 Thin film,而依材料不同可分為三類,分別為矽、化合物半導體與有機太陽能電池,其材料型態之分類如圖 1-1。目前市場上已商品化之太陽能電池大多以矽為主,這是由於其穩定性佳、製作技術已趨成熟,具有 10 年以上之使用期限,且矽原料蘊藏豐富及取材容易,至現今仍為市場主流,然而其本身光吸收係數較小,為了增加對光之吸收能量,導致元件厚度無法薄膜化(約100μm);然而薄膜太陽能電池其光電轉換效率不高,製作技術尚未成熟,未能大量商品化,然而其可製作於可撓式基板上,成本低,易大量生產,因此遠觀薄膜太陽能電池產業仍具有相當的潛力。

圖 1-1 太陽能電池種類

薄膜矽發展始於非晶矽(amorphous silicon a-Si)薄膜,於1965年由Sterling及Swann兩人第一次以射頻電漿沉積的方式由矽烷氣體解離出矽製作。1975年,英國Dunde大學的Walter Spear和Peter Le Comber在反應氣體中加入PH3或B2H6,製備出具半導體性質的非晶矽薄膜。而在當時人們對於氫原子加入非晶矽薄膜可以促成有效摻雜效能並不清楚。此摻雜技術的成功開啟了人們對此材料的廣泛注意,其原因如下:

- (a)此材料有許多特性可被應用於半導體和薄膜太陽能電池,厚度達1μm厚的 a-Si:H薄膜即可吸收約90%的太陽光能。

- (b)利用化學氣相沉積法可在低溫下(100°C~400°C)進行,且可製作於大面積。

- 1975年Triska等人證實以純的矽甲烷製作的非晶矽薄膜中亦含有氫原子,具有良好電性的非晶矽薄膜實際上是矽原子與氫原子形成的合金結構,此類非晶矽薄膜自此即被正確地稱作氫化非晶矽(Hydrogenated amorphous silicon, a-Si:H)。

- 1977年Staebler及Wronski首先指出氫化非晶矽薄膜在太陽光照射下,其費米能階(Fermi Level)會輕微的向能帶的中間移動,導致薄膜的導電率下降,而經由回火後導電率可以回復,此效應被稱為光照衰退(photodegradation)效應又稱Staebler-Wronski Effect(簡稱SWE)。

1980年Staebler 及Wronski又提出光照衰退效應主要發生在本體(bulk)內,而非在薄膜的表面,而薄膜中影響光照衰退效應的因素有很多,如雜質(碳、氧或氮)、弱鍵、氫的含量及其複雜的鍵結、非晶矽鍵結的無序性而產生的空洞或是上述因素的合成效果。

矽氫鍵結對於非晶矽薄膜太陽能電池為一重要沉膜機制的一環,SiH3被認為矽基薄膜的生長過程中的主要根種,雖然沉積過程中氫會影響基材上薄膜的生長,但SiH3的根種並不會直接與生長中的薄膜鍵結,而是擴散於薄膜表面上,並填補薄膜表面氫原子因受熱激發或被SiH3抽取而出所產生的懸鍵,故SiH3有助於薄膜的生長與品質。T.Takagi等團隊1999年指出薄膜沉膜機制中的高矽烷根種,如SiHx(dislane)、Si3Hx(trisilane)分子的組成和短生命週期的根種(SiH2)會降低薄膜品質。Noboru Nakamura、Tomonori Nishimoto、T.Takagi等團隊研究皆指出矽基薄膜太陽能器池的光衰退效應與薄膜中的SiH2的含量有關,Noboru Nakamura (1989)另指出薄膜中的缺陷數目在一特定的含量的不純物濃度下,會隨SiH2含量的增加而增加。

1987年Curtins等人於瑞士Neuchtel大學引入60MHz超高頻化學氣相沈積技術在高氫氣稀釋(SiH4+H2)條件製作μc-Si:H薄膜,使得薄膜的品質與沈積速率的控制獲得改善。VHF-PECVD的優點具有較高的電子及離子密度,但具有較低的離子能量,代表激發電漿時,離子密度增加可以提昇薄膜的沈積速率,而離子能量的降低則可減少離子對薄膜轟擊的傷害。

在太陽能電池元件文獻方面, A. Chowdhury .2008 年等人研究改變製程氣體的總流量對於薄膜結晶率與缺陷密度之影響,當總流量增加時薄膜結晶率會下降,主要是因為降低了氫原子對於薄膜表面選擇性蝕刻,致使薄膜結晶率下降。2007年 S.Y. Myong.研究團隊利用 VHF-PECVD 製作非晶矽與微晶矽轉換區間太陽能電池,研究指出在此區間的非晶矽薄膜本質層品質有較佳的穩定性與降低光衰退現象。P.D. Veneri 2008 年團隊研究指出,利用氫電漿蝕刻 p層鈍化晶粒邊界,使得p/i 界面處有緊密的接觸。實驗結果當氫蝕刻 p層 20 min 後,效率增加 20 %。2008年 F.J. Haug 等人研究非晶與微晶堆疊型太陽能電池。研究指出,在兩層元件中間加入反射層 SiO 可提高上部電池的短路電流密度,達到與下部電池電流密度的匹配。

矽薄膜太陽能電池具有低生產成本與可大面積製造等優勢,主要製程技術為電漿化學氣相沉積法(Plasma enhanced chemical vapor deposition)沉積非晶/微晶矽薄膜太陽能電池。由於矽薄膜太陽能電池元件效率仍不高,為了有效提升元件效率及降低矽薄膜太陽能電池本質層厚度與成本,故須研製光封存結構來提升太陽能電池元件效率。

## 貳、研究動機與目的

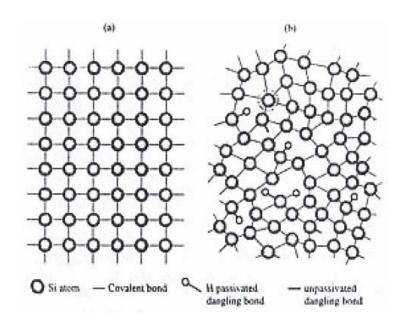

矽薄膜太陽能電池的發展始自於非晶矽薄膜,而非晶矽結構通常為無序性相位、較不穩定、毫無結晶度及導電率不佳,且經光照射後在非晶矽薄膜內所生成之懸浮鍵(Dangling bond)缺陷,會阻礙太陽能電池內生成的電子及電洞的流動,使光電轉換特性降低,稱為光劣化效應(Staebler-Wronski Effect, SWE)。為了改善這些缺點,氫化非晶轉微晶矽薄膜的研究為了取代薄膜太陽能電池中之非晶矽的本質吸收層。

圖 2-1 (a)單晶 (b)充氫非晶矽結構示意圖

改善薄膜結晶結構的方法主要是以氫氣稀釋(Hydrogen dilution)法將沈積的薄膜由非晶結構逐漸轉變至微晶矽結構,因為氫原子可以填補懸浮鍵之缺陷,蝕刻薄膜較脆弱之 Si-Si 鍵,提昇薄膜的結晶度與晶粒大小,減少懸浮鍵之比例,進而改善薄膜品質及導電特性。由文獻了解,本質層薄膜結晶比率 Xc 增加時,會降低元件效率,由相關文獻研究發現最佳的元件效率為非晶相轉微結晶相區間為最佳。

由於矽薄膜太陽能電池元件仍受限於效率,導致無法有效應用於節能市場,所以,研製光封存結構提升太陽能電池效率為重要的課題。多數國內外學者研究太陽能電池光封存結構皆以 ZnO 薄膜當作元件電極。利用 ZnO 為六方晶體結構特性形成 Texture 結構,增加入射光散射與行走路徑,進而提升元件對入射光的吸收。但因 ZnO 導電性不佳,需掺雜金屬來提高載子濃度來增加其導電特性,因而提高了製程複雜性與成本。也有多數研究學者使用糙化基板來製作太陽能電池元件,由於此基板價位不低,導致製作成本增加。2004年,A. V. Shahu, et al 提到將電極糙化處理後能增加入射光散射,如雙面電極同時糙化處理後可提高元件效率。J. Krc,

et al. 2004 年模擬出糙化處理後可提高 Haze 比例及提升元件之長波長量子效應, 另可降低元件本質層厚度。2006 年 J. A. Anna Selvan. 團隊利用 Texture TCO 與銦氧化物攙雜鉬製作於背電極部份,提升太陽能電池元件電流密度 32 %。

本研究主要分為兩個部份來探討不同的光封存結構,利用簡單與低成本的製作方式來有效的提升太陽能電池元件特性。在太陽能電池元件製作方面,我們採用 VHF-PECVD 搭載 60MHz 高頻電漿源沉積矽薄膜及太陽能電池元件,來探討不同光封存結構應用於非晶矽薄膜太陽能電池之研究。

## 参、實驗方法

#### 一、氫化矽薄膜的實驗製作流程

#### (一)製程設備

本論文所使用的製程設備為本實驗室自行設計組裝之PECVD系統,其構成分為六個系統,包含1.氣體管路系統、2.反應腔體、3.抽氣系統、4.電漿產生系統、5.進氣系統、6.介面控制系統

#### 1. 氣體管路系統

裝置反應氣體的高壓氣瓶放置於毒氣室,高毒性、高易燃性反應氣體SiH<sub>4</sub>、TMB、PH<sub>3</sub>、GeH<sub>4</sub>放置於氣瓶櫃中。不同氣體分別由各自的不鏽鋼氣體管路導入混何氣體管路之後,再流入反應腔體中。反應氣體流量由質量流量控制器所控制進入反應腔體流量。

#### 2.反應腔體

腔體中央為一個直立式可上下調整的不鏽鋼平板下電極,電極的尺寸為直徑 23cm圓形平板,下電極部份由PID控溫器做加熱控溫。反應氣體在氣體管路中經過混合後,由上電極shower head的部份流入,腔體內部的壓力控制由壓力控制器配合蝴蝶閥來控制。

#### 3.抽氣系統

此系統使用Dry 幫浦做為抽真空及製成抽氣,包括有毒及爆炸性氣體的特殊氣體,並提供無法於低真空度下運作的Turbo pump前級抽氣。高真空幫浦為Turbo pump,反應腔體的背景壓力達到10<sup>-6</sup>以確認無外漏之虞後,再開啟主腔體與load lock之間的閥門利用機械手臂將試片送入。

#### 4.電漿產生系統

本系統使用的是超高頻電漿產生系統,電漿頻率為AE  $60MH_Z$ 提供功率  $0\sim2000W$ 。

#### 5. 進氣系統

系統所使用的氣體分別為SiH<sub>4</sub>、TMB、PH<sub>3</sub>、GeH<sub>4</sub>、CH<sub>4</sub>、CF<sub>4</sub>、H<sub>2</sub>及O<sub>2</sub>。反應器氣體分別有各自的不鏽鋼管路導入混合氣體管路混合均勻後再進入腔體。

#### 6.介面控制系統

與人機介面控制氣體管路抽氣與進氣閥門開關、流量設定控制與讀取、設定 PID溫控器溫度以及製程壓力控制。

#### (二)實驗氣體與材料

矽甲烷氣體(SiH<sub>4</sub>)

氫氣(H<sub>2</sub>)

三甲基硼(TMB)

氫化磷(PH3)

四氟化碳(CF<sub>4</sub>)

氧氣(O<sub>2</sub>)

素玻璃基板(3.9cm×3.9cm)

矽晶圓基板(silicon wafer)

金屬遮罩(metal mask)

鋁錠(aluminum target)

#### (三)基板的清洗

- 1. 先將ITO玻璃基板以中性清潔劑搓洗

- 2. 使用丙酮(acetone)在超音波震洗機內震洗8分鐘

- 3. 使用異丙醇(Isopropanol)在超音波震洗機內震洗8分鐘

- 4. 使用去離子水(DI water)在超音波震洗機內震洗8分鐘

- 5. 再利用氮氣(N<sub>2</sub>)槍將基板吹乾

6. 最後放置烤箱內,以100℃之溫度軟烤8分鐘去除水氣。

#### (四)氫化矽薄膜沉積

將已經烘乾之試片,以高耐熱之真空膠帶固定在石墨電極板上,在放至傳送箱(load lock)中進行粗抽,做沈積薄膜前的準備。將製程中各實驗參數(腔體壓力、基板溫度、射頻功率、氣體流量)設定後,開啟需要沈積的氣體流量,並持續抽氣至設定的壓力到達穩定後,再依實驗所需的沈積時間,開啟電漿開始沈積薄膜。將已經沈積之太陽能電池元件,送至金屬蒸鍍系統中蒸鍍金屬陰極。本實驗室金屬蒸鍍系統使用熱阻式鎢舟做為加熱源,利用電流大小來控制蒸鍍速率,而金屬薄膜之厚度則是使用石英震盪器來量測。

#### 二、太陽能電池元件製作流程

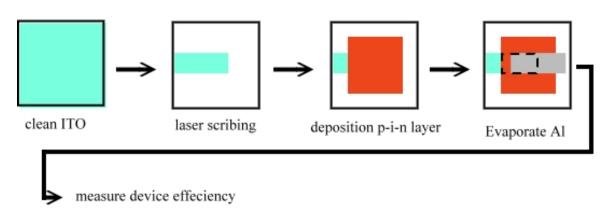

將清潔過後的ITO玻璃放入雷射雕刻機雕刻,設定雕刻功率、速度與頻率後進行雕刻。雕刻所需的陽極圖案後,再清潔一次ITO以去除表面粉塵。清潔完後,放入PECVD系統中,利用金屬遮罩沉積p-i-n薄膜,再放置金屬蒸鍍系統中蒸鍍鋁電極即完成薄膜太陽能電池元件,元件製作流程如圖3-1。

圖 3-1 矽薄膜太陽能電池元件製作流程

#### 三、光封存結構製作流程

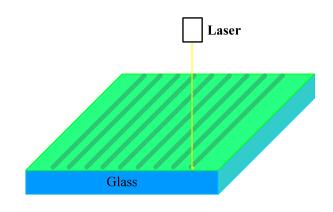

#### (一).ITO 電極雷射雕刻處理

本實驗室雷射雕刻機型號為 YVO4 使用雷射雕刻機波長為 1064nm,將 ITO 基板分別由上述清洗基板步驟進行清潔,接著放入雷射雕刻機平台進行所需圖樣雕刻以達到糙化效果。藉由調變雷射雕刻機不同參數如掃描速率、雷射功率與掃描間距以避免擊穿 ITO 薄膜因而影響元件表現。將雷射雕刻後的基板再進行清潔與烘乾,最後放入電漿化學氣相沉積系統(PECVD)沉積太陽能電池元件。圖 3-2 為雷射雕刻示意圖。

圖 3-2 雷射雕刻示意圖

#### (二)微結構薄膜壓印

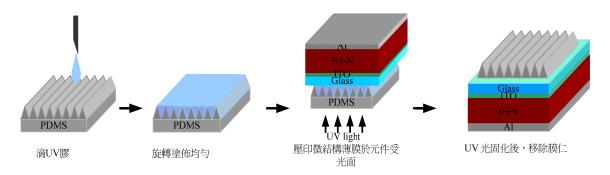

微結構壓印技術研究中,首先將製作完成的太陽能電池元件玻璃受光表面清除乾淨,再將製作好的微結構模具旋塗 UV 膠,將元件受光面部份壓印在 UV 膠上,接者使用 UV 曝光機曝光 20 秒硬化後,再把模具移除。元件製作流程如圖 3-3。

圖 3-3 微結構薄膜壓印製作流程

## 肆、實驗結果與討論

#### 一、調變本質層射頻功率對太陽能電池元件之研究

本實驗是固定沈積壓力為1.5 Torr、及基板溫度為250℃的製程條件下,改變不同功率下的本質層對於元件特性之影響。

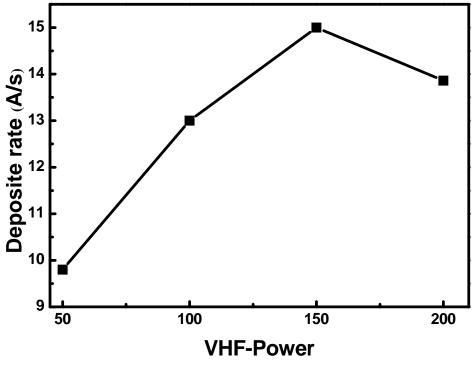

沉積速率測試方面,由圖4-1中我們可以發現當電漿功率由50W提高到150W時,沉積速率隨之上升,但當功率繼續提高至200W時沉積速率反而下降,是因為在電漿反應系統裡,自由基(反應前驅物)到基板位置形成沉積效應(Deposition),但當電漿中帶能量之離子會對基板造成轟擊效應(Bombardment),當功率從50W增加至150W時,電漿解離反應氣體SiH4形成自由基數量也會增加,沉積效應大於轟擊效應,致使沉積速率增加。但當電漿功率增大至200W時,電漿中離子之轟擊效應增強,造成薄膜沉積速率下降。因此,在薄膜沉積過程當中也伴隨著轟擊作用,所以控制電漿功率達到最佳值可使薄膜沉積速率提升。

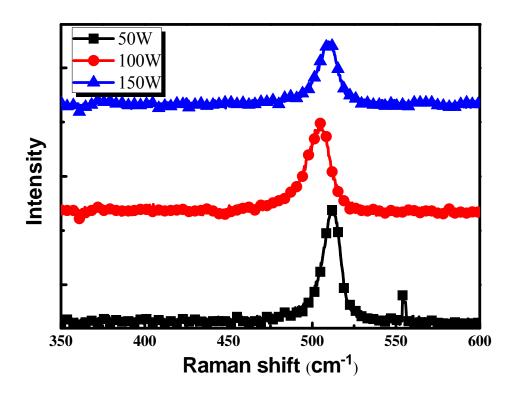

分析結晶度方面 $(X_C)$ ,依照圖4-2拉曼分析圖顯示,Raman光譜峰值都落於 $510 \text{cm}^{-1}$ 位置,我們判斷當電漿功率增加時,轟擊效應大於 $H^+$ 選擇性蝕刻效應,導致薄膜在隨機轟擊下結晶率也跟著下降,導致Raman吸收峰值隨之下降。

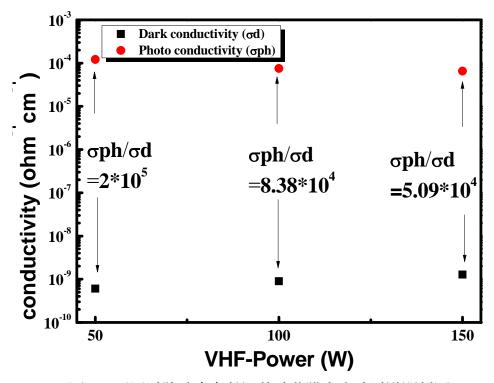

電特性方面,由圖4-3顯示矽薄膜在不同電漿功率下之光電導與暗電導分析。 在矽薄膜光電導特性中,我們可以了解到矽膜受光後產生電子電洞對的變化,由 於矽薄膜受光後產生的能量造成電子電洞分離,使得電導值提升,所以光電導值 提升越多越適合製作太陽能電池元件,本實驗所沉積出光暗電導比值約在10<sup>5</sup>左 右,比值越高代表矽薄膜對光的頻譜響應越好。當射頻功率持續增加,因轟擊作 用導致矽薄膜品質降低,致使光暗電導比值下降。

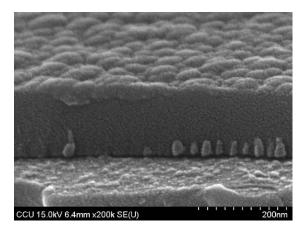

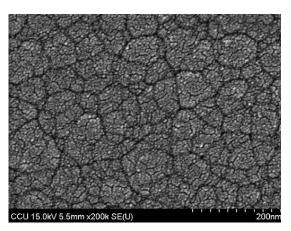

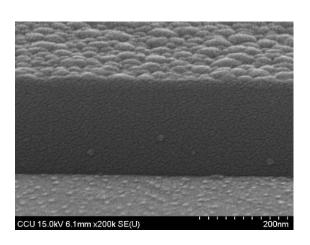

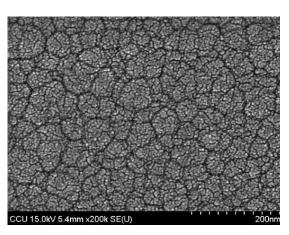

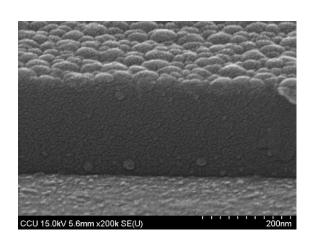

圖4-4為使用SEM量測不同電漿功率沉積矽薄膜的表面與剖面圖,由圖可看出表面出現奈米結晶(Nano-Crystalline)情況。隨著功率增加,奈米結晶的團聚現象反而減小,這個現象的主因應該是如上述功率增大至一定程度時產生的轟擊效應,使得矽薄膜表面接受轟擊所造成結晶下降。

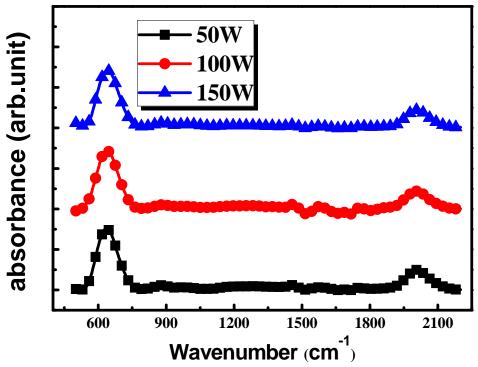

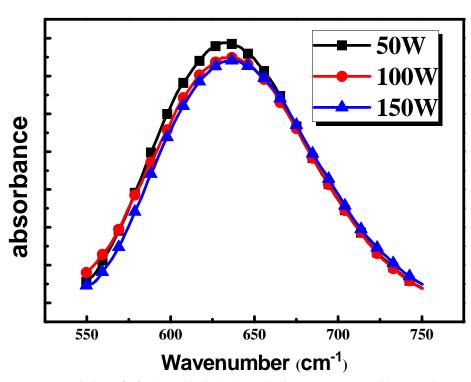

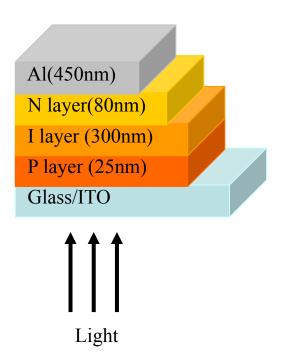

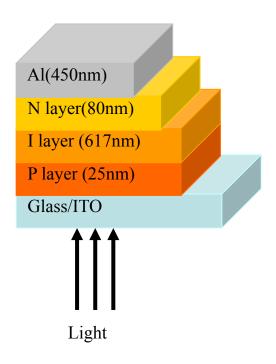

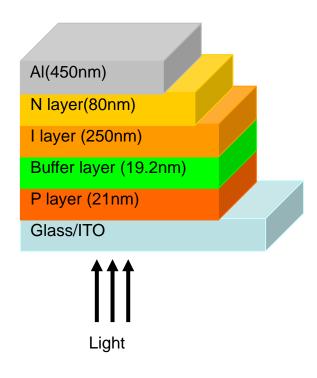

FTIR量測薄膜沉膜特性分析方面圖4-5為調變不同功率下FTIR圖,當功率越大氫含量有下降的趨勢,是因為H<sup>+</sup>對矽薄膜選擇性蝕刻的緣故,當功率越高H<sup>+</sup>擁有足夠的能量到達薄膜表面進行蝕刻,打斷薄膜內部較弱的Si-Si鍵結或Si-H鍵結,或帶走薄膜中的氫與H<sup>+</sup>形成氫氣而離開薄膜,因而造成薄膜氫含量下降。由圖4-6中630~640cm<sup>-1</sup>的搖擺模,可以估算出薄膜中的氫含量。太陽能電池元件特性上,我們固定P-layer、N-layer與本質層厚度部分結構如圖4-7,將不同電漿功率沉積本質

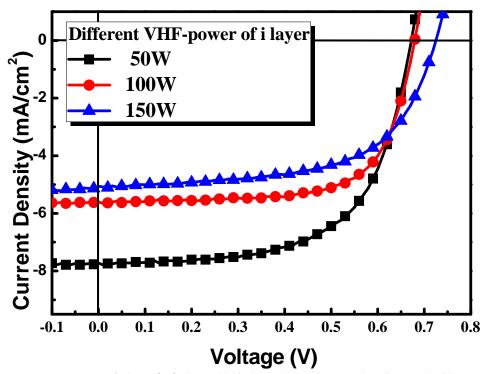

層來探討對於太陽能電池元件效率之影響,元件製作參數如表4-1。表4-2為太陽能電池元件特性,包含開路電壓、短路電流、填充因子與效率,當電漿功率使用50W時,有最佳的元件效率,開路電壓:0.67(V)、短路電流:7.72(mA/cm²)、FF:62%、轉換效率:3.24%。由表4.2.6所示短路電流隨著功率增加而減少,主要是因為由上述光暗電導比值中提到,當射頻功率增加時光暗電導比值因薄膜表面所受到轟擊效應增加,使光暗電導比值隨功率上升而下降,導致短路電流有下降的趨勢因而影響元件效率。圖4-8為太陽能電池元件J-V特性曲線圖。

表4-1 不同電漿功率參數沉積本質層薄膜之元件製作參數

|         | Pressure | Temp.  | VHF power | SC(%) | Yp(%)  | Yn(%) | Total flow (sccm) |

|---------|----------|--------|-----------|-------|--------|-------|-------------------|

| P layer | 1.5torr  |        | 35W       | 1%    | 0.002% | X     | 520               |

| I layer | 1.5torr  | 250 °C | 50-150W   | 5%    | X      | X     | 400               |

| N layer | 1.2torr  |        | 50W       | 1%    | X      | 0.05  | 520               |

表4-2 不同電漿功率參數沉積本質層薄膜之元件特性

| VHF-power | $V_{oc}(V)$ | $J_{sc}(mA/cm^2)$ | FF(%) | Eff.(%) |

|-----------|-------------|-------------------|-------|---------|

| 50        | 0.67        | 7.72              | 62    | 3.24    |

| 100       | 0.68        | 5.59              | 68    | 2.62    |

| 150       | 0.71        | 5.06              | 61    | 2.26    |

圖4-1 不同電漿功率參數沉積矽薄膜之沉積速率關係圖

圖4-2 不同電漿功率參數沉積矽薄膜之拉曼光譜圖

圖4-3 不同電漿功率參數沉積矽薄膜之光暗電導關係圖

(a)50W

(b)100W

(c) 150W

圖4-5 不同電漿功率參數沉積矽薄膜之FTIR圖

圖4-6 不同電漿功率參數沉積矽薄膜吸收峰630-640cm-1搖擺模之FTIR圖

圖4-7 不同電漿功率參數沉積本質層薄膜之元件結構圖

圖4-8 不同電漿功率參數沉積本質層薄膜之太陽能電池IV曲線圖

#### 二、調變P層摻雜濃度對太陽能電池元件之研究

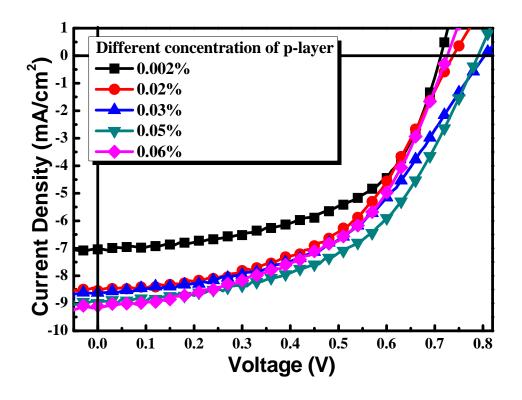

本實驗是使用上述最佳參數I層功率為50W與上一小節矽氫稀釋比(SiH<sub>4</sub>/(SiH<sub>4</sub>+H<sub>2</sub>)為5%及固定N層、基板溫度為250℃下改變P層摻雜濃度對於元件之影響。

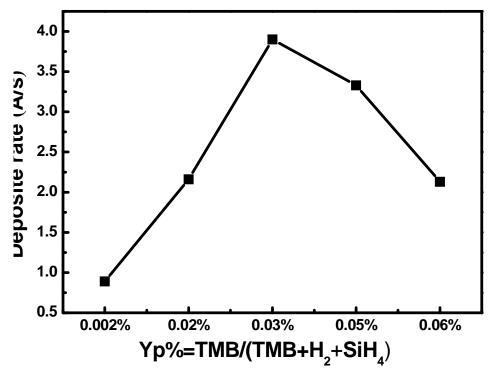

測試沈積速率方面,改變不同濃度摻雜比Yp(TMB/(SiH<sub>4</sub>+H<sub>2</sub>+TMB))為 0.002%~0.06%,並固定沈積時間為5分鐘,在利用表面輪廓儀量測到膜厚後,將膜厚除以沈積時間,即可求出沈積速率(Å/s),如圖4-9為改變不同摻雜比Yp與沈積速率關係圖顯示,由圖可看出當摻雜濃度增加時,薄膜沈積速率稍微增加,但當摻雜濃度超過0.03%後,由於大量的TMB氣體影響了SiH<sub>4</sub>鍵結,因而沉積速率有下降的趨勢。

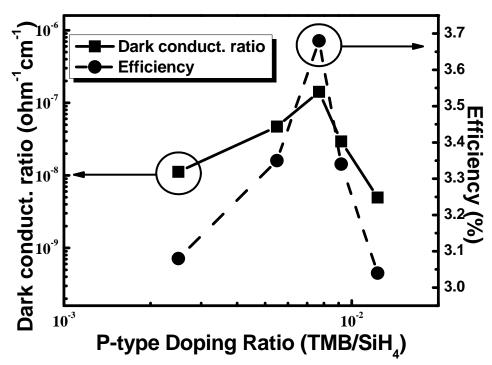

薄膜電特性分析,量測P型暗電導分析,如圖4-10得知在摻雜約0.05%左右有較高的暗電導值,經由我們製作太陽能電池元件結構圖4-11發現,當暗電導值越高時有較佳的元件效率,元件製作參數如表4-3。在開路電壓 $V_{oc}$ 方面因為TMB摻雜增加,因而拉開了內建電場 $V_{b}$ ,導致開路電壓有些許增加如表4-4,圖4-12為太陽能電池元件J-V量測結果。

表 4-3 不同 TMB 濃度摻雜比 Yp 之元件製作參數

|         |          |        |           |       | •           |       |                   |

|---------|----------|--------|-----------|-------|-------------|-------|-------------------|

|         | Pressure | Temp.  | VHF-power | SC(%) | Yp(%)       | Yn(%) | Total flow (sccm) |

| P layer | 1.5torr  |        | 35W       | 1%    | 0.002~0.06% | X     | 520               |

| I layer | 1.5torr  | 250 °C | 50W       | 5%    | X           | X     | 400               |

| N layer | 1.2torr  |        | 50W       | 1%    | X           | 0.05  | 520               |

表 4-4 不同 TMB 濃度摻雜比 Yp 之元件特性

| $Yp(TMB/(SiH_4+TMB+H_2)$ | $V_{oc}(V)$ | $J_{sc}(mA/cm^2)$ | FF(%) | Eff.(%) |

|--------------------------|-------------|-------------------|-------|---------|

| 0.002%                   | 0.71        | 7.03              | 55.8  | 2.79    |

| 0.02 %                   | 0.74        | 8.54              | 50    | 3.21    |

| 0.03 %                   | 0.8         | 8.63              | 48.6  | 3.35    |

| 0.05 %                   | 0.79        | 8.99              | 51    | 3.68    |

| 0.06%                    | 0.73        | 9.09              | 50    | 3.34    |

圖 4-9 改變不同摻雜比 Yp 之沉積速率

圖 4-10 改變不同摻雜比 Yp 之暗電導與元件效率

圖4-11 改變不同摻雜比Yp之元件結構圖

圖4-12 改變不同摻雜比Yp之元件J-V特性曲線

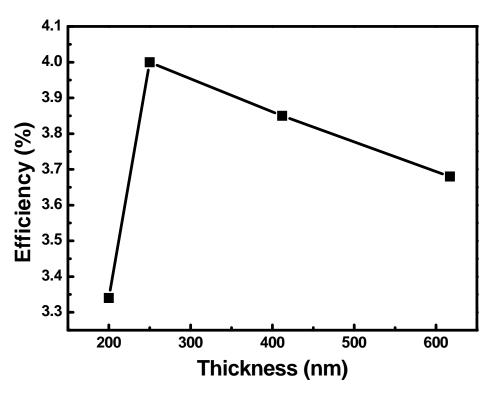

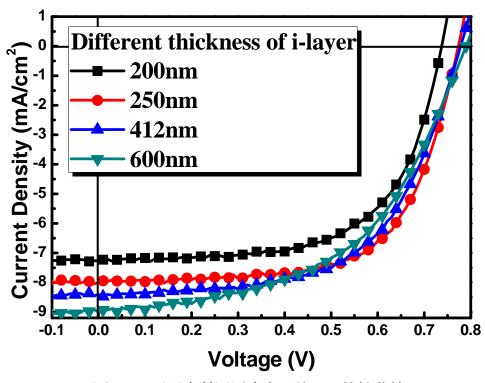

#### 三、不同本質層厚度對於元件效率之研究

本實驗是使用上述最佳參數I層功率為50W、矽氫稀釋比(SiH<sub>4</sub>/(SiH<sub>4</sub>+H<sub>2</sub>)為5%、固定P/N層參數與基板溫度為250℃下改變I層厚度對於元件之影響,表4-5為本質層I層沉積參數。

由圖 4-13 效率與厚度關係圖了解到,當本質層厚度為 200nm 時,因元件本質層受光後所產生的電子電洞數量較少,因而短路電流密度較低,造成元件效率不高。當元件本質層厚度為 250nm 時,有最佳的元件特性表現,元件效率為 4%,如表 4-6。但是,當元件本質層厚度超過 250nm 後,雖然受光後產生的電子電洞數量增加,提升了短路電流密度,但因過後的本質層會導致受光後產生的電子電洞擴散至該電極的過程中容易被缺陷捕捉,因而提高了復合電流與串聯電阻,致使太陽能電池元件功率因子(FF)與特性下降。圖 4-14 為太陽能電池元件 J-V 量測結果。

表4-5 元件本質層沉積參數

| I layer thickness(nm) | Pressure | Temp.  | VHF-power | SC(%) | Total flow (sccm) |

|-----------------------|----------|--------|-----------|-------|-------------------|

| 200                   |          |        |           |       |                   |

| 250                   | 1 Storr  | 250 °C | 35W       | 5%    | 520               |

| 412                   | 1.5torr  | 230 C  | 33 W      | 370   | 320               |

| 600                   |          |        |           |       |                   |

表 4-6 不同本質層厚度之元件特性

| I layer thickness(nm) | $V_{oc}(V)$ | $J_{sc}(mA/cm^2)$ | FF(%) | Eff.(%) |

|-----------------------|-------------|-------------------|-------|---------|

| 200                   | 0.74        | 7.26              | 62.3  | 3.34    |

| 250                   | 0.77        | 8                 | 65    | 4       |

| 412                   | 0.78        | 8.4               | 58.8  | 3.85    |

| 600                   | 0.79        | 8.99              | 51    | 3.68    |

圖 4-13 不同本質層厚度與元件效率關係圖

圖 4-14 不同本質層厚度之元件 J-V 特性曲線

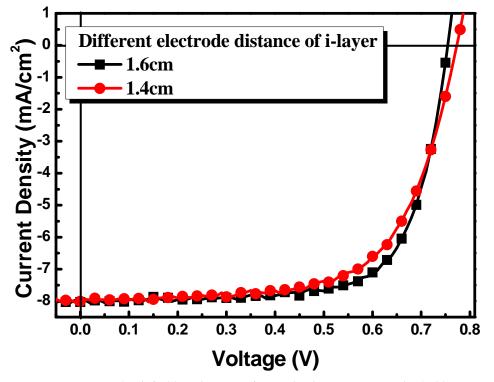

#### 四、不同電極距離製作本質層對於元件效率之影響

本實驗是使用上述最佳參數I層電漿功率50W、厚度250nm、矽氫稀釋比(SiH<sub>4</sub>/(SiH<sub>4</sub>+H<sub>2</sub>)為5%、固定P/N層參數與基板溫度為250℃下改變I層電極距離對於元件之影響,表4-7為本質層I層沉積參數。

由於電漿化學氣相沉積系統(PECVD)擁有較高的離子能量,對於矽薄膜沉積的過程中扮演了很大的影響角色,過強的離子轟擊會擊穿薄膜形成缺陷導致薄膜品質降低,因而影響到元件效率的表現。因此本章節研究為增加本質層電極距離,降低其離子轟擊於 P層,由圖 4-15 元件 J-V 特性曲線圖發現,當本質層電極距離增加後,元件 J-V 曲線有較好的功率因子(FF)。由表 4-8 元件特性了解到功率因子(FF)有較大的提升幅度,也提升了元件效率由 4%至 4.29%。

表4-7 元件本質層沉積參數

| Electrode distance(cm) | Pressure | Temp.  | VHF-power | Total flow (sccm) |

|------------------------|----------|--------|-----------|-------------------|

| 1.8                    | 1.5torr  | 250 °C | 35W       | 520               |

| 1.6                    | 1.5011   | 230 C  | 33 W      | 320               |

表 4-8 不同本質層厚度之元件特件

| Electrode distance(cm) | $V_{oc}(V)$ | $J_{sc}(mA/cm^2)$ | FF(%) | Eff.(%) |

|------------------------|-------------|-------------------|-------|---------|

| 1.8                    | 0.75        | 8.02              | 71.3  | 4.29    |

| 1.6                    | 0.77        | 8                 | 65    | 4       |

圖 4-15 成長本質層之不同電極距離之元件 J-V 特性曲線

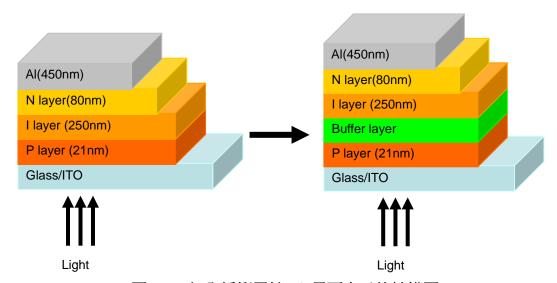

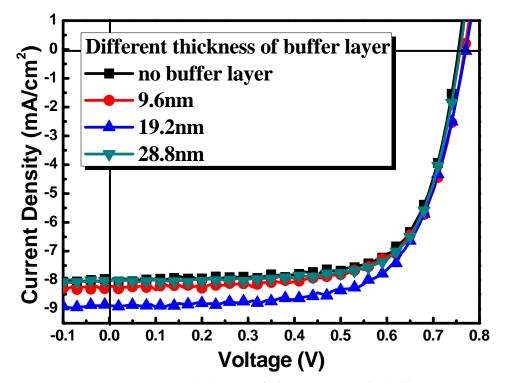

#### 五、加入不同厚度緩衝層於 p/i 界面對於元件效率之研究

本實驗是使用上述最佳參數I層電漿功率50W、厚度250nm、矽氫稀釋比 (SiH<sub>4</sub>/(SiH<sub>4</sub>+H<sub>2</sub>)為5%、固定P/N層參數與基板溫度為250℃下加入緩衝層於P/I界面 之間對於元件之影響,圖4-16為太陽能電池元件結構圖,元件參數如前述最佳參數 加入緩衝層,表4-9為緩衝層沉積參數。

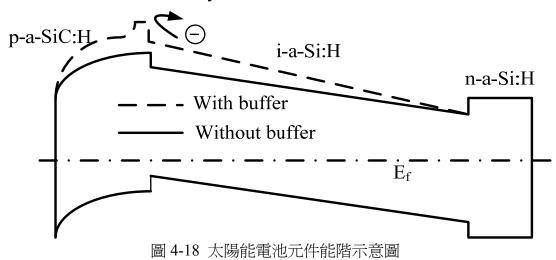

主要探討 p/i 介面緩衝層厚度對非晶矽薄膜分析及元件特性分析,如表 4-10 為不同緩衝層厚度之矽薄膜太陽能電池特性,圖 4-17 為 p/i 介面緩衝層厚度之矽薄膜太陽能電池元件 J-V 曲線。緩衝層主要阻擋 I 層因受光後產生的電子進入,因而與電洞復合,產生復合損失電流如圖 4-18 所示,當緩衝層厚度為 9.6 nm 時,緩衝層過薄導致些微提升元件之短路電流密度。當厚度為 28.8 nm 時,因過厚之緩衝層使元件整體之串聯電阻增加,導致元件電流密度下降。

表4-9 元件緩衝層沉積參數

| Buffer layer thickness(nm) | Pressure | Temp. | VHF-power | SC(%) | Total flow (sccm) |

|----------------------------|----------|-------|-----------|-------|-------------------|

| 9.6                        |          |       |           |       |                   |

| 19.2                       | 1.5Torr  | 250°C | 35W       | 1%    | 520               |

| 28.8                       |          |       |           |       |                   |

表 4-10 不同緩衝層厚度之元件特性

| Buffer layer thickness(nm) | $V_{oc}(V)$ | $J_{sc}(mA/cm^2)$ | FF(%) | Eff.(%) |

|----------------------------|-------------|-------------------|-------|---------|

| X                          | 0.75        | 8.02              | 71.3  | 4.29    |

| 9.6                        | 0.77        | 8.22              | 69    | 4.39    |

| 19.2                       | 0.77        | 8.88              | 67    | 4.59    |

| 28.8                       | 0.76        | 8.05              | 71    | 4.38    |

圖 4-16 加入緩衝層於 P/I 界面之元件結構圖

圖 4-17 不同緩衝層厚度之元件 J-V 特性曲線

## i-a-Si:H buffer layer

#### 六、不同光封存結構對於矽薄膜太陽能電池之影響

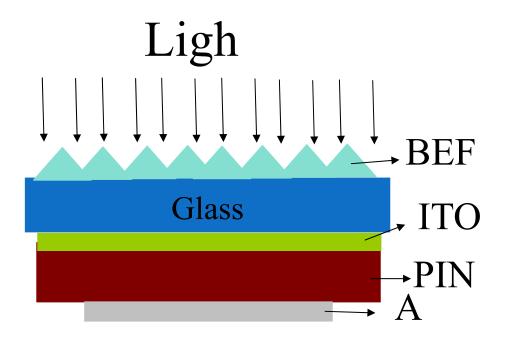

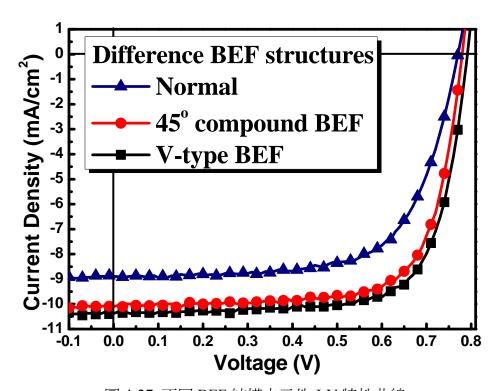

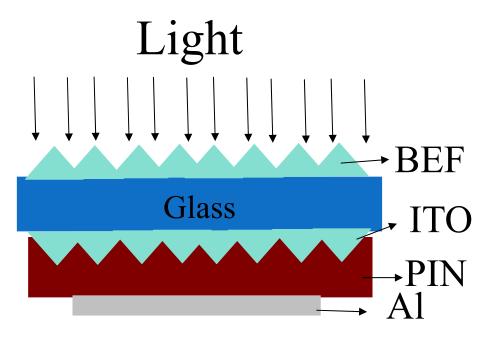

本實驗為使用不同光封存結構對矽薄膜太陽能電池影響之探討,由文獻中了解到提升太陽能電池吸光效率的方法,一般都利用透明導電膜ZnO:Al 製作Texture 結構,增加光散射與降低反射率的作用,故在一般太陽能電池應用上有顯著提升。本章節研究中,分別使用了兩種不同方法的光封存結構,來提升元件的入射光捕捉,提升元件效率。表4-11為太陽能電池元件沉積參數,圖4-19為太陽能元件結構。

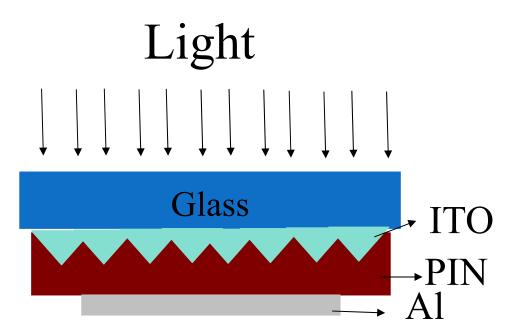

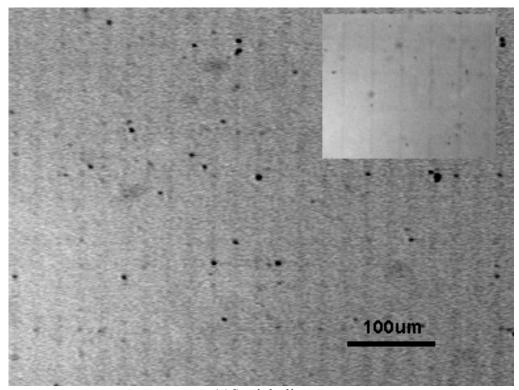

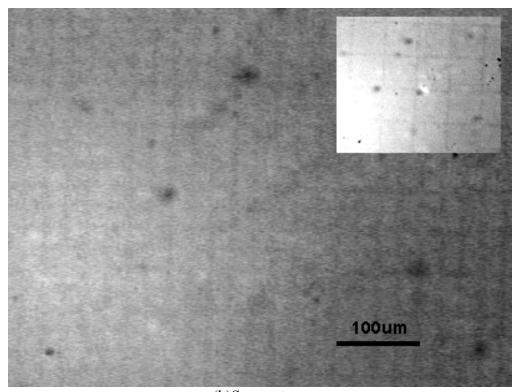

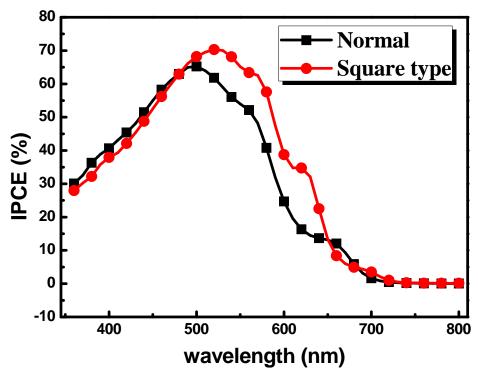

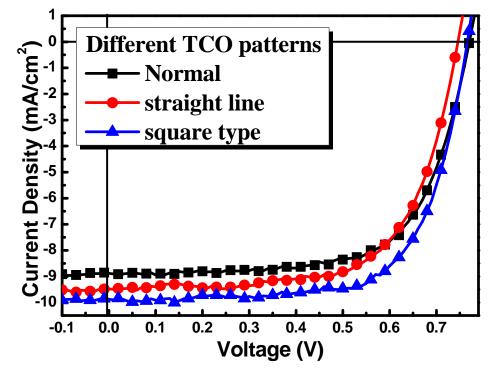

第一部份是研究TCO糙化的部份,本研究是利用雷射雕刻機波長為1064nm對陽極ITO進行所需的圖樣雕刻,圖4-20為結構示意圖。調變掃描速率與雷射功率以避免擊穿ITO薄膜因而影響元件效率,表4-12為雷射雕刻參數。主要探討ITO電極表面經過雷射糙化處理後光捕捉效果,我們雕刻了直線(straight line)與方型(square type)圖樣如圖4-21為光學顯微鏡(OM)下所拍攝的不同雕刻圖樣。由表4-13元件特性得知,最佳糙化圖樣為方型圖樣結構,提升了短路電流由8.88 mA/cm²增加至9.87 mA/cm²,效率由4.59 %提升至5.19 %,效率提升約13 %,由圖4-22 IPCE圖了解到,ITO糙化後能增加長波長吸收,致使元件效率提高。圖4-23為不同ITO糙化圖案之元件IV特性曲線圖。

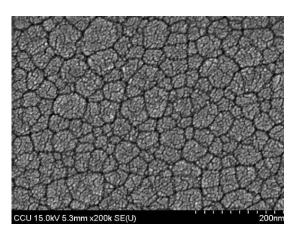

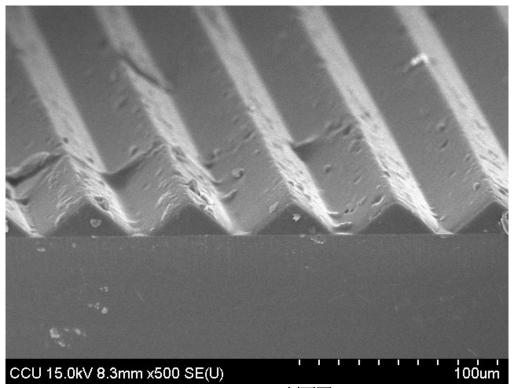

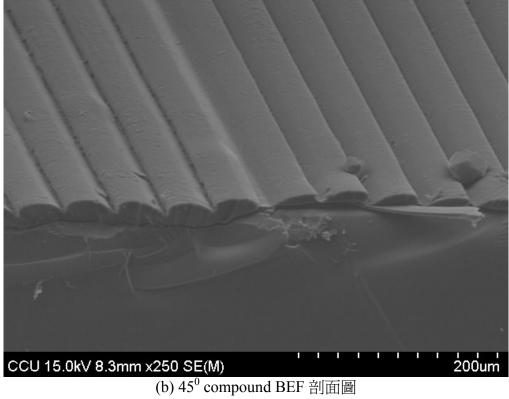

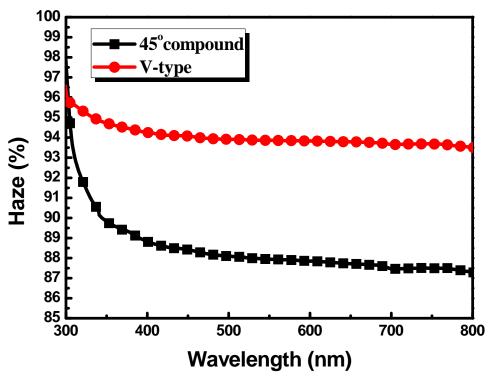

第二部份是在玻璃基板上添加光封存結構brightness enhancement film (BEF)如圖4-24為玻璃基板受光面微結構壓印示意圖。製作不同光封存結構來探討對於元件效率的影響,圖4-25為SEM拍攝剖面圖,由於改變了光源進入玻璃基板後由原本的直向光改變成散射光,隨著光封存結構增加散射光與內反射,可以有效增加光在主動層行走的路徑,進而提高太陽能電池元件效率,此方法能以較簡單的壓印製程方式達到提升效率的結果。由表4-13可知,使用V-type、45度複合膜與無光封存結構之元件比較下,V-type光封存結構有最佳的元件效率,由圖4-26Haze量測中得知,V-type有最佳的糙化結果,因而增加了光在元件行走之路徑,提升短路電流由8.88 mA/cm²增加至10.37 mA/cm²,效率由4.59 %提升至5.99 %。使用V-type光封存結構後效率提升了30%,圖4-27為不同光封存結構之元件IV特性曲線圖。

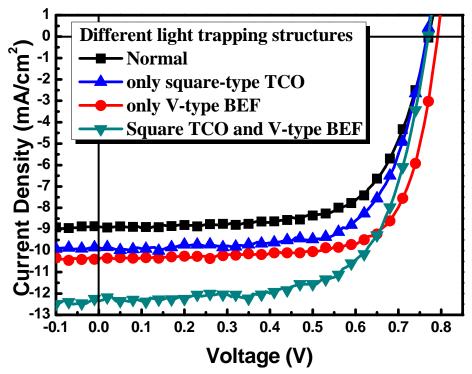

第三部份為將兩結構結合,將ITO以最佳方形糙化圖樣與V-type微結構薄膜壓印應用於太陽能電池元件,圖4-28為兩種結構結合示意圖。將兩種光封存結構結合提升了短路電流由8.88 mA/cm²增加至12.35 mA/cm²,效率由4.59 %提升至6.29 %。使用雙光封存結構後效率提升了37%。圖4-29為不同最佳光封存結構之元件J-V特性曲線圖。

表4-11 太陽能電池元件沉積參數

|              | Pressure | Temp.  | VHF-power | SC(%) | Yp(%) | Yn(%) | Total flow (sccm) |

|--------------|----------|--------|-----------|-------|-------|-------|-------------------|

| P layer      | 1.5torr  |        | 35W       | 1%    | 0.05% | X     | 520               |

| Buffer layer | 1.5torr  | 250 °C | 50W       | 1%    | X     | X     | 1000              |

| I layer      | 1.5torr  |        | 50W       | 5%    | X     | X     | 400               |

| N layer      | 1.2torr  |        | 50W       | 1%    | X     | 0.05  | 520               |

表4-12 ITO雷射雕刻參數

| 雷射功率 | 掃描速率 | 間距    | 掃描次數 | 頻率    |

|------|------|-------|------|-------|

| 72%  | 900  | 0.005 | 1    | 30KHz |

表 4-13 不同 ITO 雷射糙化圖樣之元件特性

| ITO pattern   | BEF structure | $V_{oc}(V)$ | $J_{sc}(mA/cm^2)$ | FF(%) | Eff.(%) |

|---------------|---------------|-------------|-------------------|-------|---------|

| normal        | normal        | 0.77        | 8.88              | 67    | 4.59    |

| Straight line | normal        | 0.75        | 9.48              | 65    | 4.64    |

| Square type   | normal        | 0.77        | 9.87              | 68.3  | 5.19    |

| normal        | 45° compound  | 0.78        | 10.1              | 72.2  | 5.69    |

| normal        | V-type BEF    | 0.79        | 10.37             | 73    | 5.99    |

| Square type   | V-type BEF    | 0.77        | 12.35             | 66    | 6.29    |

圖 4-19 太陽能電池之元件結構圖

圖4-20 雷雕ITO圖樣化結構示意圖

(a)Straight line

(b)Square type

圖4-21 光學顯微鏡(OM)下不同ITO雷射雕刻圖樣(a) Straight line(b)Square type

圖 4-22 雷雕 ITO 方形圖樣之 IPCE 圖

圖 4-23 不同雷雕 ITO 圖樣之元件 IV 特性曲線

圖 4-24 BEF 壓印結構示意圖

(a)V-type BEF 剖面圖

圖 4-25 不同 BEF 結構壓印之 SEM 圖(a)V-type BEF (b) 450 compound BEF

圖 4-26 不同 BEF 結構 Haze 量測圖

圖 4-27 不同 BEF 結構之元件 J-V 特性曲線

圖 4-28 兩種光封存結構結合示意圖

圖 4-29 兩種光封存結構結合之元件 IV 特性曲線

### 伍、結論

- (一) 當VHF功率越高時,非晶矽薄膜沉積速率也會越來越高,主要原因是在電漿中的反應氣體解離後,隨著VHF功率的增強而增加了SiH4成自由基的數量,因此使得非晶矽薄膜沉積速率越快。

- (二)隨著功率增加,奈米結晶的團聚現象反而減小,這個現象的主因應該是如上 述功率增大至一定程度時產生的轟擊效應,使得矽薄膜表面接受轟擊所造成 結晶下降。

- (三) 功率越大氫含量有下降的趨勢,是因為H<sup>+</sup>對矽薄膜選擇性蝕刻的緣故,當功率越高H<sup>+</sup>擁有足夠的能量到達薄膜表面進行蝕刻,打斷薄膜內部較弱的Si-Si鍵結或Si-H鍵結,或帶走薄膜中的氫與H<sup>+</sup>形成氫氣而離開薄膜,因而造成薄膜氫含量下降。

- (四) 當射頻功率持續增加,因轟擊作用導致矽薄膜品質降低,致使光暗電導比值下降。當射頻功率為50W時有最佳的光暗電導比值10<sup>5</sup>已達元件級標準,元件效率由2.26 %提升至3.24 %,短路電流密度由5.06 mA/cm<sup>2</sup>提升至7.72 mA/cm<sup>2</sup>。

- (五) P層碳化矽之暗電導隨著摻雜濃度增加而增加,使元件之內建電場較大驅使短路電流及開路電壓提升。當摻雜濃度為0.05%時有最佳暗電導率及元件效率:  $V_{oc}$ =0.79 V、 $J_{sc}$ =8.99 mA/cm<sup>2</sup>、F.F.=51 %及效率3.68 %。

- (六) 當本質層厚度增加時產生之電子電洞對也增加。當本質層厚度為200 nm時,因光照射元件後本質層產生電子電洞對較少,導致產生元件電流密度較低。當厚度為至412~617 nm時,雖增加元件之短路電流密度,也增加元件等效電路之串聯電阻,導致元件之FF降低,進而整體元件效率降低。當本質層厚度為250 nm時有元件最佳特性:Voc=0.77V, Jsc=8 mA/cm², FF=65 %及Eff.=4 %。

- (七) 過強的離子轟擊會擊穿薄膜形成缺陷導致薄膜品質降低,因此本章節研究為增加本質層電極距離,降低其離子轟擊於P層,提升太陽能電池元件特性,功率因子(FF)有較大的提升幅度,效率由4%至4.29%。

- (八) 緩衝層主要降低p層與i層之間產生復合損失電流,當緩衝層厚度為 $9.6\,\mathrm{nm}$ 時,緩衝層過薄導致些微提升元件之短路電流密度。當厚度為 $28.8\,\mathrm{nm}$ 時,因過厚之緩衝層使元件整體之串聯電阻增加,導致元件電流密度下降。當緩衝層厚度為 $19.2\,\mathrm{nm}$ 時,有元件最佳特性: $V_{\mathrm{oc}}$ =0.77V,  $J_{\mathrm{sc}}$ = $8.88\,\mathrm{mA/cm}^2$ , FF= $67\,\%$ , Eff:= $4.59\,\%$ 。

(九) 運用兩種光封存結構應用於薄膜太陽能電池,分別為雷射雕刻ITO圖樣與簡單的壓印方式製作光封存結構在玻璃基板上,改變光源經過光封存結構後其光路徑由原本的垂直通過改變成散射,此現象意味光在主動層的移動路徑增加,因而提高光電流。雷雕ITO糙化提升短路電流8.88 mA/cm²至9.87 mA/cm²,元件開路電壓為0.77V、填充因子為68.3%、效率由4.59提升至5.19%,效率提升約13%。微結構BEF為V-type有最佳的元件特性表現,短路電流由8.88 mA/cm²增加至10.37 mA/cm²,元件開路電壓為0.79 V、填充因子為73%、效率由4.59%提升至5.99%,提升了30%。將兩種最佳結構結合後,短路電流由8.88 mA/cm²增加至12.35 mA/cm²,元件開路電壓為0.77 V、填充因子為66%、效率由4.59%提升至6.29%。使用雙光封存結構後效率提升了37%。

## 陸、參考文獻

黄信雄,1997。「氣候變化綱要公約」;太陽能學刊 第2卷第一期。

Sterling H.F. and Swann R.C.G, 1965. Chemical vapor deposition promoted by r.f. discharge, solid-state Electron,8(8),653.

Spear W. E and Comber P. G Le, 1975. Substitutional doping of amorphous silicon, Solid State Communications, Vol 17, pp1193-1196.

Spear W. E. and Comber P. Le, 1976. Electronic properties of substitutionally doped amorphous Si and Ge, Philosophical Magazine, Vol 33, pp935-949.

Triska A., Dennison D. and Fritzsche H., Bull. Am. Phy. Soc, 1975. Vol 20, pp39

Staebler D. L. and Wronski C. R., 1977. Reversible conductivity changes in discharge-produced amorphous Si, Appl. Phys. Lett, Vol.31, pp.292

Staebler D.L. and Wronski C.R., 1980. Optically induced conductivity changes in discharge-produced hydrogenated amorphous silicon, J. Appl. Phys. 51, 3262-3268.

Guha S. and Yang J., 1992. Effect of microvoids on initial and light-degraded efficiencies of hydrogenated amorphous silicon alloy solar cells, Appl. Phys. Lett. 61, pp.1444-1446.

Bruno G., Capezzuto P., and A. Madan, 1995. Plasma deposition of amorphous silicon-based materials, Academic Press.

Takagi T., Hayashi R., Ganguly G., Kondn M., 1999. A. Matsuda, Thin Solid Films 345, p75-79

Nakamura etc N., 1989. Jpn. J. of Appl. Phys. v28, 10 Oct., p1762.

Nishimoto T., Takai M., Miyahara H., Kondo M. and Matsuda A., 2002. Journal of Non-Crystalline Solids 299–302 1116–1122

Poortmans J and Arkhipov V. Thin Film Solar Cell, IMEC, Leuven, Belgium, CH5.

Street R. A., 1991. Hydrogenated Amorphous Silicon, Cambridge University Press, New York.

Shah A., Sauvain E., Wyrsch N., Curtins H, Leutz B., Shen D.S., Chu V., Wagner S., Schade H., Chao H. W. A., 1988. a-Si:H films deposited at high rates in a 'VHF' silane plasma: potential for low-cost solar cells, Electron Lett, Vol.1, pp282-287.

Chowdhury A., 2008. Effect of gas flow rates on PECVD-deposited nanocrystalline silicon thin film and solar cell properties, Solar Energy Materials & Solar Cells 92

385-392

Myong S.Y., 2008. Silicon-based thin-film solar cells fabricated near the phase boundary by VHF PECVD technique, Solar Energy Materials & Solar Cells 92 639-645.

Veneri P.D., 2008. Influence of microcrystalline silicon bottom cell on micromorph tandem solar cell performance, Thin Solid Films 516 6979-6983.

Haug F. J., 2009. Development of micromorph tandem solar cells on flexible low-cost plastic substrates, Solar Energy Materials & Solar Cells 93 884-887.

Shah A. V., Schade H., Vanecek M., Meier J., Vallat-Sauvain E., Wyrsch1 N., Kroll U., Droz C., and Bailat J., 2004. "Thin-film Silicon Solar Cell Technology", PROGRESS IN PHOTOVOLTAICS: RESEARCH AND APPLICATIONS, Vol.12, (), 113-142.

Tauc J., 1968. Optical properties and electronic structure of amorphous Ge and Si, Materials Research Bulletin, Vol.3, pp.37-46.

Stutzmann M., Biegelsen D. K. and Street R. A., 1987. Phys. Rev. B, Vol.35, pp.5666-5701.

Son J. I., 2010. Effect of substrate temperature on the nanostructural and chemical features of nc-Si:H thin films prepared by PECVD, Current Applied Physics.

Mukherjee C., 2001. Growth of device quality p-type  $\mu$  c-Si:H films by hot-wire CVD for a-Si pin and c-Si heterojunction solar cells, Thin Solid Films 395 310-314.

Anna Selvan J. A., Delahoy Alan E., Sheyu Guo and Yuan-Min Li, 2006. A new light trapping TCO for nc-Si:H solar cells, Solar Energy Materials & Solar cells, pp.903371-3376.

Krc J., Smole F. and Topic M., 2004. Study of enhanced light scattering in microcrystalline silicon solar cells, Journal of Non-Crystalline Solids, Vol.338–340, 673–676.

Anna Selvan J.A., 2006. A new light trapping TCO for nc-Si:H solar cells, Solar Energy Materials & Solar Cells 90 3371 3376